# 國立臺北大學電機工程學系專題報告

## 應用在手機擴音器之 D 類放大器

# A Class D Amplifier for Mobile Phone

組員:邱宇萱

指導老師: 黃弘一 老師

執行期間:104年7月至105年6月

#### 1. 摘要

- The transistors in traditional linear amplifier like Class A and Class AB amplifier which operate in active region for BJT or in saturation region for MOSFET have the good operation linearity, but the efficiency is relatively low due to the power consumption of the output stage transistor.

- The switching mode amplifier

meaning the output stage transistors

operate in fully off/on state like

Class D amplifier has less power

consumption and get higher

operation efficiency; however, the

switching mode leads poor linearity

comparing to the linear amplifier.

- On the basis of the power saving, the switching mode amplifiers are more suitable for portable device.

關鍵字: classD,FDCMPWM

#### 2. 專題進行方式

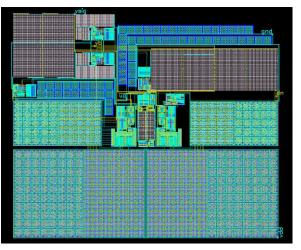

本專題主要是利用 Hspice 這個模 擬軟體來模擬電路,同時透過 waveview 這款軟體來觀察訊號,此專 題為一人獨立完成並會與實驗室學長 與同學們討論,並在每周的 meeting 與 老師討論進度,時間允許的話,會完成 下線晶片所有程序,最終完成 PCB 板 將晶片進行量測,完成整個 IC 設計的 程序。

#### 3. 主要成果與評估

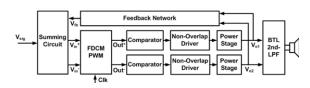

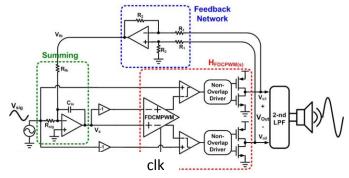

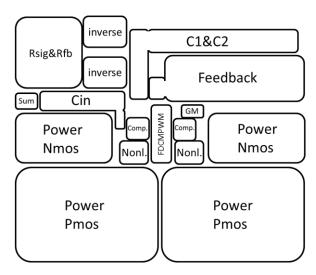

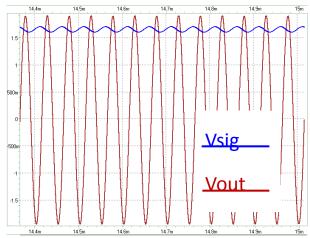

圖 6-1 為所提出 D 類放大器整體系統 方塊圖,FDCPWM Stage 輸入由 Summing Circuit 來的 In<sup>+</sup>和 In 訊號,產 生一組只與 In<sup>+</sup>和 In 相關的差動 PWM 訊號(Out<sup>+</sup>、Out<sup>-</sup>),此差動訊號經由兩 個比較器與與輸入訊號(Vsig)以及輸入 的反向訊號(Vsig\_bar)相比較產生 0 或 1 的大訊號,而比較器的兩個輸出訊號再 經由兩組非重疊輸出級驅動器產生出 的非重疊訊號來驅動輸出的功率晶體 (Power Stage)。 BTL(Bridge Tied Load) 二階低通濾波器濾除高頻成份而將低 頻的音頻輸出至揚聲器。

為了提升線性度,此架構使用了負回

授技巧來降低系統操作之 THD(Total Harmonic Distortion)。其操作如下,Feed-Back Network 將輸出級的脈寬 差動輸出(Vo1、Vo2)由運算放大器產生 一單端訊號  $V_{fb}$ ,此單端訊號進入 Summing Circuit 與  $V_{sig}$  作負相加,利 用負回授將非線性因素扣除後所產生的  $In^+$ 和  $In^-$ 訊號再進入 FDCPWM Stage 去做調變。

而為避免被動元件受製程因素影響電路操作,影響時脈訊號 Clk 的電容將與FDCPWM 所負載的電容成比例關係以達到較好的線性度。

圖 6-1 所提出系統方塊模型圖

# 6.2 全差動電流控制脈波寬度調變器(FDCPWM)

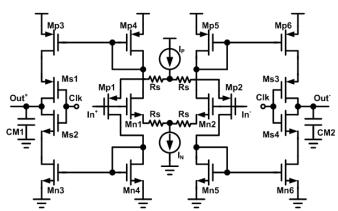

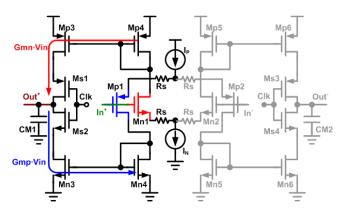

圖 6-2 為全差動電流式脈波寬度調 變器(FDCPWM)示意圖,其操作原理基本 上是將差動輸入電壓轉導成一組差動電流, 而這組差動電流再分別對兩個電容進行充 放電,進而產生一組由輸入訊號來控制脈 波寬度的差動訊號。

電路中的 Mp1、Mn1、Mp2 以及 Mn2 為輸入級,Mn1 將 In<sup>+</sup> 轉導成 VIn<sup>+</sup>G<sub>mn</sub> 的電流,Mp1 將 In<sup>+</sup> 轉導成-VIn<sup>+</sup>G<sub>mp</sub> 的電流,Mn2 將 In<sup>-</sup> 轉導成 VIn<sup>-</sup>G<sub>mn</sub> 的電流,Mp2 將 In<sup>-</sup> 轉導成-VIn<sup>-</sup>G<sub>mp</sub> 的電流。當 Clk=0 時,電流鏡 Mp3、Mp4 將電流 VIn<sup>+</sup>G<sub>mn</sub>對電容 CM1 進行充電,電流鏡 Mp5、Mp6 將電流 VIn<sup>-</sup>G<sub>mn</sub> 對電容 CM2 進行充電,當 Clk=1 時,電流鏡 Mn3、Mn4 將電流-VIn<sup>+</sup>G<sub>mp</sub> 對電容 CM1 進行放電,電流鏡 Mn5、Mn6 將電流-VIn<sup>-</sup>G<sub>mp</sub> 對電容 CM1 進行放電。

圖 6-2 FDCPWM 電路示意圖

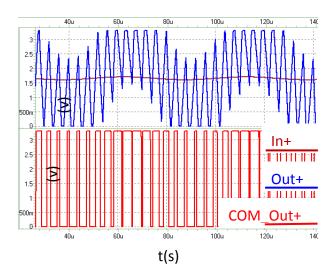

左邊半電路的充放電流組 VIn+Gmn、

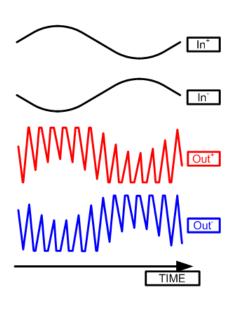

-VIn<sup>+</sup>G<sub>mp</sub> 和右邊半電路的充放電流組 VIn<sup>-</sup>G<sub>mn</sub>、-VIn<sup>-</sup>G<sub>mp</sub> 彼此為差動模式,在 Clk 切換時,分別各對左右兩半電路之電 容進行充放電,進而產生一對 Out<sup>+</sup>和 Out<sup>-</sup> 的電壓訊號,由於左右兩半電路是差動的 充放電電流組而造成 Out<sup>+</sup>和 Out<sup>-</sup>也彼此為 差動的電壓訊號,圖 6-3 即為輸入訊號 In<sup>+</sup> 和 In<sup>-</sup> 以及其對應的 Out<sup>+</sup>和 Out<sup>-</sup>電壓 訊號。

圖 6-3 FDCPWM 輸出訊號示意圖

# 6.3 FDCPWM 理論分析

由於 FDCPWM 電路為左右對稱架構, 因此在此以左半電路進行分析。另外,原 本應該是要將  $Out^+$ 與  $In^+$ 做比較,為了簡 化分析,在此將  $In^+$ 替換成其 ac 準位  $V_{eff,0}$ 。 如圖 6-4,考慮一輸入訊號  $\text{In}^+$ ,當  $\text{In}^+$  為  $V_1$  時,Mn1 的有效轉導電壓為  $V_a$  而 Mp1 的有效轉導電壓為  $V_b$ 。 當  $\text{In}^+$ 為  $V_2$  時,Mn1 的有效轉導電壓為  $V_b$  而 Mp1 的有效轉導電壓為  $V_b$  而 Mp1 的有效轉導電壓為 ,其中  $V_1\text{+}V_2 = V_{DD}$ ,  $(V_a\text{+}V_b)/2\text{=}V_{eff,0}$ 。

圖 6-4 FDCPWM 半電路操作示意圖

# 6.4 非重疊閘極驅動器

### (Non-Overlapping Gate-Driver)

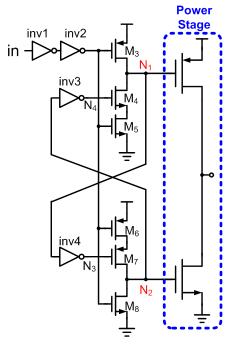

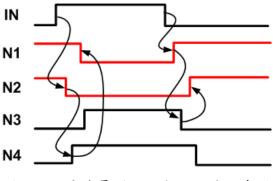

圖 6-13 為非重疊閘極驅動器電路[6], 其主要功能為提供一組非重疊訊號  $N_1$  和  $N_2$  分別提供給輸出級的 Power PMOS 和 Power NMOS。

其操作原理及過程如圖 6-14,當訊號 IN 由 0 轉 1,使得 NMOS  $M_8$  導通因此節點  $N_2$  電壓被強迫拉到 Gnd 而其反向訊號  $N_4$  就轉為 VDD 而將 NMOS  $M_4$  導通使得節點  $N_1$  電壓被強迫拉到 Gnd 而其反向訊號  $M_3$  就轉為  $M_4$  以  $M_5$  以  $M_7$  關閉。當

訊號 IN 由 1 轉 0,使得 PMOS  $M_3$  導通因此節點  $N_1$  電壓被強迫拉到 VDD 而其反向訊號  $N_3$  就轉為 Gnd 而將 PMOS  $M_7$  導通使得節點  $N_2$  電壓被強迫拉到 VDD 而其反向訊號  $N_4$  就轉為 GND 將 NMOS  $M_4$  關閉。

如此操作下,節點電壓 N1 和節點電壓 N2 將因 inv3 和 inv4 的延遲時間而有一小段錯開時間,可以保證下一級 Power Stage 中的 Power PMOS 和 Power NMOS 絕對不會再同一時間導通,因此在 switching 過程中不會有貫穿電流(short current)由 VDD 直接到 GND,因此可以提升 D 類放大器的操作效率。

在此電路設計時有兩件事需要注意,第一,此電路對於 Power Stage 的驅動能力要適當,若其驅動能力太大會使得Power Stage 在轉態時的電流變化量太大而造成 Ground Bounce 效應而增加在VDD和 GND上的雜訊量。但驅動能力若太小會造成 Power Stage 的轉態延遲時間過大而增加 switching loss 使整體線性度下降。

第二, inv3 和 inv4 的延遲時間要適當 拿捏,延遲時間太大會造成 Dead Time 過 大而降低取樣解析度進而使線性度下降, 延遲時間若小於 Power Stage 的轉態延遲 時間則還是會使得 Power PMOS 和 Power NMOS 再同一時間導通,而失去此電路的功能。

圖 6-13 非重疊閘極驅動器電路示意圖

圖 6-14 非重疊閘極驅動器訊號示意圖

# 6.5 輸出級 (Output Stage)

輸出級為一個 Power PMOS 和 Power NMOS 所組成,當 Power PMOS 導通時

Power NMOS 關閉而對輸出濾波器充電, 當 Power NMOS 導通時 Power PMOS 關閉 而對輸出濾波器放電。

# 6.6 輸出濾波器 (Output Filter)

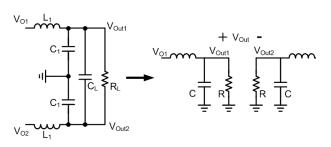

由於所提出之D類放大器的輸出為差動訊號,因此所採用的輸出濾波器為BTL(Bridge Tied Load)的二階低通濾波器,如圖 6-15 所示。其功用在於將高頻的取樣頻率濾除但保留音頻的訊號帶再輸出至喇叭。

圖 6-15 二階低通濾波器

由於聲音的頻寬為 20Hz~20KHz,因 此在設計此濾波器的截止頻率就為 20KHz。其分析如下,將圖 6-15 左邊的電 路圖化成右邊的等效模型,其中,

$$V_{out 1} = \frac{R || sC^{-1}}{sL + (R || sC^{-1})} \times V_{o1}$$

$$(6-16)$$

$$V_{out 2} = \frac{R || sC^{-1}}{sL + (R || sC^{-1})} \times V_{o2}$$

(6-17)

由(6-16)(6-17)可得:

$$V_{out} = (V_{out 1} - V_{out 2}) = (V_{o1} - V_{o2}) \times \frac{1}{LCs^2 + \frac{L}{R}s + 1}$$

(6-18)

由(6-18)可得:

$$T_{\text{Filter}} \; \left( \; S \; \right) \; = \; \frac{V_{\text{out}}}{V_{\text{ol}} - V_{\text{o2}}} \; = \; \frac{1}{LCs^{-2} + \frac{L}{R}S + 1} \; = \; \frac{1}{\left( \frac{S}{\omega_0} \right)^2 + \left( \frac{1}{Q \times \omega_0} \right) S + 1} \; . \label{eq:total_filter}$$

(6-19)

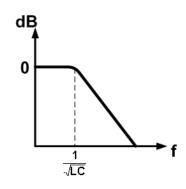

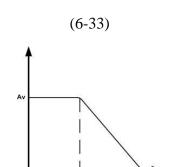

其中,截止頻率如圖 6-16, $\omega_0 = \frac{1}{\sqrt{LC}}$ ;

$$Q = R \times \sqrt{\frac{C}{L}}$$

;  $R = \frac{R_L}{2}$ ;  $C = 2C_L + C_1$ ;  $L = L_1$ °

圖 6-16 二階低通濾波器截止頻率

# 6.7 回授網路 (Feedback Network)

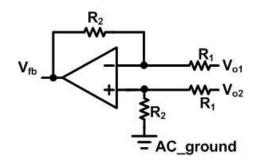

圖 6-17 回授網路示意圖

圖 6-17 為架構中所使用的回授網路, 其功能在於將兩個系統差動輸出 V01 和 V02 經由運算放大器轉成單端輸出  $V_{fb}$ ,此 訊號為聲音訊號  $V_{sig}$  的反向訊號。而在 Summing Circuit 中將會把  $V_{fb}$ 和  $V_{sig}$ 相加 再進入 FDCPWM Stage 中再做訊號的調 變。

由於兩個系統差動輸出 Vo1 和 Vo2 為 大訊號而且含有調變頻率與聲音頻率,為 了產生與聲音訊號  $V_{signal}$  的反向訊號  $V_{fb}$  , 因此基本上此回授網路為具有濾波和增益 調整的功能。其分析如下:

$$V_{fb} = A_{v}(V^{+} - V^{-})$$

(6-20)

$$V^{+} = \frac{R_{2}}{R_{1} + R_{2}} \times V_{o2}$$

(6-21)

$$V^{-} = \frac{R_{2}}{R_{1} + R_{2}} \times V_{o1} + \frac{R_{1}}{R_{1} + R_{2}} \times V_{fb}$$

(6-22)

由式(6-20)(6-21)(6-22) 得:

$$V_{fb} \times \left(1 + A_v \frac{R_1}{R_1 + R_2}\right) = A_v (V_{o2} - V_{o1}) \frac{R_2}{R_1 + R_2}$$

(6-23)

因此由(6-23)式可得:

$$\beta = T_{\text{Feedback (s)}} = \frac{V_{\text{fb}}}{\left(V_{\text{o2}} - V_{\text{o1}}\right)} = \frac{R_2}{R_1}$$

(6-24)

# 6.8 兩級式運算放大器 (Two Stage Operational Amplifier)

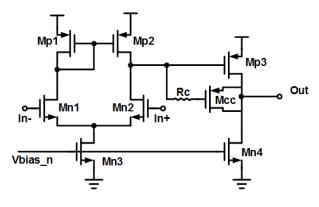

圖 6-18 兩級式運算放大器

圖 6-18 為整體系統架構中所使用的

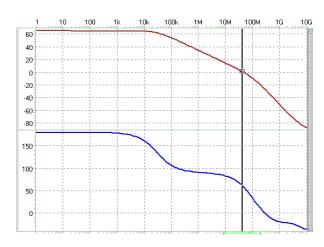

兩級式運算放大器,由於其高增益以及高 輸出擺幅而使用此種架構的放大器。而兩 級式放大器若未做頻率補償其實是屬於雙 極點放大器,若把一個雙極點放大器應用 成運算放大器的話會有穩定度的問題,為 了解決這個問題,在此使用 Rc 和 MOS 電 容做頻率補償,補償後可由表 6-1 兩級式 運算放大器的規格以及圖 6-19 兩級式運 算放大器之小訊號波德圖中看到,其相位 邊界為 60.3 度,因此為一個穩定的單極點 放大器。

圖 6-19 兩級式運算放大器小訊號波德圖

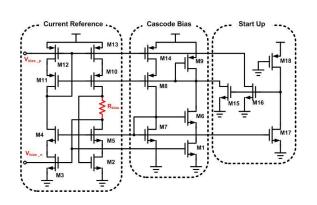

# 6.9 電流產生器(Constant Gm)

圖 6-20 為一個 constant gm 電流產生器,此種電流產生器 VDD 偏移和溫度偏移的免疫能力,因此可提供系統中的運算放大器以及比較器一個穩定的偏壓電流,

其 gm 只跟 Rbias 有關,換句話說其 gm 與電壓源及環境溫度呈獨立關係,所以它能夠用來當作穩定的電流源。

圖 6-20 constant gm 電流產生器

# 6.10 系統轉移函數(System

# **Transfer Function**)

圖 6-21 系統內部細節圖

圖 6-21 為系統內部細節圖,由於此系 統為閉迴路系統,在此節將討論其系統的 轉移函數。首先,此架構為差動訊號輸出, 其系統輸出可表示為:

$$V_{out} = V_{o1} - V_{o2}$$

$$(6-25)$$

Vo1 可表示為:

$$V_{o1} = -V_s \times H_{FDCPWM}$$

(s)

$$(6-26)$$

Vo2 可表示為:

$$V_{o2} = V_s \times H_{FDCPWM}$$

(s)

(6-27)

由(6-26)(6-27) 系統輸出可表示為:

$$V_{out} = -2V_s \times H_{FDCPWM}$$

(s)

$$(6-28)$$

回授訊號 Vfb 可表示為:

$$V_{fb} = (V_{o2} - V_{o1}) \times \beta = -V_{out} \times \beta$$

(6-29)

其中β =

$$\frac{R_2}{R_4}$$

在此 Summing Circuit 將聲音訊號  $V_{sig}$ 和回授訊號  $V_{fb}$  作 superposition 的相加則 其輸出  $V_s$ 可表示成:

$$V_{s} = \frac{-\left(\frac{R_{in}}{R_{sig}}V_{sig} + \frac{R_{in}}{R_{i}}V_{tb}\right)}{\left(1 + \frac{s}{\omega_{2}}\right)} = \frac{-\left(\frac{R_{in}}{R_{sig}}V_{sig} + \frac{R_{in}}{R_{i}}\beta\right)}{\left(1 + \frac{s}{\omega_{2}}\right)}$$

$$= \frac{-R_{in} \cdot V_{sig}}{R_{sig}\left(1 + \frac{s}{\omega_{2}}\right)} + \frac{R_{in} \cdot R_{2} \cdot V_{out}}{R_{i} \cdot R_{1} \cdot \left(1 + \frac{s}{\omega_{2}}\right)}$$

$$(6-30)$$

其中

$$\omega_2 = \frac{1}{R_{in}C_{in}}$$

將(6-30)式代回(6-28)可得系統輸出

Vout 為:

$$V_{out} = -2 \left[ \frac{-R_{in} \cdot V_{sig}}{R_{sig}} + \frac{R_{in} \cdot R_{2} \cdot V_{out}}{R_{f} \cdot R_{1}} \right] \cdot H_{FDCPWM} \quad (s)$$

(6-31)

整理後可得:

$$V_{out} \cdot \left[ 1 + \frac{R_{in} \cdot R_2 \cdot V_{out} \cdot H_{FDDPWM} \quad (s)}{R_i \cdot R_1 \cdot \left( 1 + \frac{s}{\omega_2} \right)} \right] = \frac{2 \cdot R_{in} \cdot V_{sig} \cdot H_{FDDPWM} \quad (s)}{R_{sig} \cdot \left( 1 + \frac{s}{\omega_2} \right)}$$

$$(6-32)$$

再將式(6-32)整理後可得整個系統的

轉移函數 Tsystem(s), 可表示為:

$$T_{\text{system (s)}} = \frac{V_{\text{out}}}{V_{\text{sig}}} = \frac{\frac{2 \cdot R_{\text{in}} \cdot H_{\text{FDCPWM}} \quad \text{(s)}}{R_{\text{sig}} \left(1 + \frac{S}{\omega_2}\right)}}{1 + \frac{2 \cdot R_{\text{in}} \cdot R_2 \cdot H_{\text{FDCPWM}} \quad \text{(s)}}{R_{\text{f}} \cdot R_1 \cdot \left(1 + \frac{S}{\omega_2}\right)}}$$

$$= \frac{\frac{2 \cdot R_{\text{f}} \cdot R_{\text{1}}}{R_{\text{sig}} \cdot R_{\text{2}}}}{\left(1 + \frac{\text{S}}{\omega_{\text{2}}}\right) + \frac{R_{\text{f}} \cdot R_{\text{1}}}{2 \cdot R_{\text{sig}} \cdot R_{\text{2}} \cdot H_{\text{FDCPWM}} \quad \text{(s)}}$$

圖 6-22 整體迴路之波德圖

圖 6-22 為整體閉迴路之波德圖,整體電路 為單極點的系統,其閉迴路增益為

$$Av = \frac{R_{fb}}{R_{sig}}$$

-3dB 點 f1 為:

$$f1 = \frac{1}{2\pi R_{fb}C_{in}}$$

### 4. 結語與展望

- FDCMPWM has proved the pulse width variation is a linear function of input signal

- FDCMPWM using constant bias current to gain a constant transconductance GM so it can effectively degrade the effect of process variation

- A Class D audio amplifier with feedback network has the better linearity performance

### 5. 銘謝

感謝這一年來,所有學長與老師的陪 伴。必須承認大三這一年因為專題製作讓 我認識了黃老師,我人生中認識最重要的 老師,他改變了我對很多事物的看法,同 時也讓我在學習上可以有新的想法,新的 突破在思考很多事物上都會有嶄新的想法, 謝謝這一年所有陪伴我走過這段路的人, 由衷感謝。