# 國立臺北大學電機工程學系 103 學年度學生專題製作計畫書

任意責任週期之同步映射延遲電路

# **Arbitrary Duty Cycle Synchronous Mirror Delay**

組員:

學號:410187014 姓名:陳信甫

指導老師:黃弘一 老師

中華民國 104年 02月 1日

## 壹、計畫摘要

在現在電路應用中,例如 SDRAM 是使用外部電路來改變記憶體內部的狀態。由 於輸入緩衝器和輸出驅動器會造成內部訊號和外部訊號之間的時脈偏斜,因此若 是想要增加記憶體的效能就必須消除此時脈偏斜,但是當系統的操作時脈越來越 高,傳統的同步映射延遲電路在可操作頻率範圍有著許多限制。

關鍵字:相位同步、同步延遲、同步映射延遲

### 貳、背景及目的

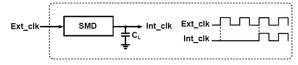

在某些電路應用例如 SDRAM,就是使用外部電路來改變記憶體內部的狀態。因為外部訊號進入到電路內部時,必須經過 Input Buffer 以及 Output Driver 來驅動晶片內的電路,兩者皆會造成延遲時間。當電路內部訊號跟外部訊號有著 Input Buffer 以及 Output Driver 所造成的 Clock Skew 時,會降低電路操作的效能,所以我們必須減低此 Clock Skew,就有了同步映射延遲電路的應用,如下圖所示。

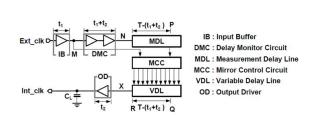

下圖為一傳統的同步映射延遲電路(Synchronous Mirror Delay Circuit),圖中的延遲監控電路(Delay Monitor Circuit, DMC)用來補償 Input Buffer 和 Output Driver 所產生的延遲時間  $t_1$ 和  $t_2$ ,再經過量測延遲電路(Measured Delay Line, MDL) 複製控制(Mirror Control Circuit, MCC)以及可調延遲電路(Variable Delay Line, VDL)的單位延遲元件所組成的延遲鏈之後如圖。

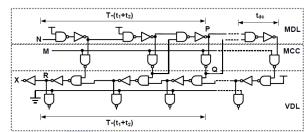

基本電路如下,假設輸入一個 Ext\_clk 訊號週期為 T,在 Input Buffer (IB) 和 Output Driver (OD) 各產生  $t_1$ 和  $t_2$ 延遲時間時,DMC 就必須補償  $t_1$ 和  $t_2$ 延遲時間。當訊號 N 經過多個 MDL 延遲之後的訊號 P,在 MCC 中的 NAND 閘正好和訊號 M 的第二個週期重疊,因此從 N 延遲到 P 需要時間  $T-(t_1+t_2)$ ,並產生一個與訊號 P 完全相反的訊號 Q,如圖。之後此訊號會在 VDL 中也走相同的延遲路徑長度  $T-(t_1+t_2)$ 。如此一來,整體電路輸入訊號抵達輸出時的延遲時間就為  $t_1+(t_1+t_2)+T-(t_1+t_2)+T-(t_1+t_2)+t_2=2T$ ,也就是在兩個週期之後,輸入和輸出訊號就會同步,如下面的時序圖和波形圖。

#### 參、儀器設備需求表

電腦: HSpice、SPICE Explorer。

#### 肆、預期完成之工作項目及具體成果

- 1. 閱讀 SMD 論文,了解、比較與模擬不同的 SMD 的架構。

- 2. 目前已有方法能增加操作頻率,但必須犧牲些許的週期來達成鎖定,若是可以找到 更佳的方式來增加操作頻率,且不會增加鎖定週期,如此電路利用的方向會更廣。

- 3. 在減少相位誤差方面,若是有辦法在不增加細調動作的鎖定週期下,能更快且更準確的達成減少相位誤差,也會是未來努力的方向。

- 4. 若能重新設計路徑控制電路,找出如何平衡低頻高頻的操作範圍,將雙方可操作範圍最大化,也是非常值得努力的目標。

#### 伍、預定進度甘梯圖

請視計畫性質及需求自行訂定。

| 月次         | 第   | 第           | 第        | 第   | 第   | 第           | 第           | 第        | 第           | 第           | 第           | 第        |

|------------|-----|-------------|----------|-----|-----|-------------|-------------|----------|-------------|-------------|-------------|----------|

|            | 1   | 2           | 3        | 4   | 5   | 6           | 7           | 8        | 9           | 10          | 11          | 12       |

| 工作項目       | 月   | 月           | 月        | 月   | 月   | 月           | 月           | 月        | 月           | 月           | 月           | 月        |

| 基本訓練       | >   | <b>&gt;</b> |          |     |     |             |             |          |             |             |             |          |

| 資料及文獻收集    |     |             | <b>V</b> | >   | >   | >           | >           |          |             |             |             |          |

| 架構構思       |     |             |          |     |     | <b>&gt;</b> | <b>&gt;</b> |          |             |             |             |          |

| 電路模擬       |     |             |          |     |     |             | <b>V</b>    | <b>V</b> | <b>&gt;</b> |             |             |          |

| 報告撰寫       |     |             |          |     |     |             |             |          |             | <b>&gt;</b> | <b>&gt;</b> | <b>V</b> |

| 進度累計百分比(%) | 10% | 20%         | 25%      | 30% | 35% | 40%         | 50%         | 60%      | 80%         | 85%         | 90%         | 100%     |

### 陸、參考文獻

- [1] 李昆樺,具寬頻操作之同步映射延遲電路,2010。

- [2] T. Saeki, Y. Nakaoka, M. Fujita, et al., "A 2.5-ns Clock Access, 250-MHz, 256-Mb SDRAM with Synchronous Mirror Delay," IEEE J. Solid-State Circuits, vol. 31, no. 11, pp. 1656-1665, Nov. 1996.

- [3] Sei Hyung Jang, "A new synchronous mirror delay with an auto-skew-generation circuit," IEEE ISCAS, Vol. 5, pp. 397-400, May. 2003.

- [4] K. Sung, B.-D. Yang, and L.-S Kim, "Low power clock generator based on an area-reduced interleaved synchronous mirror delay scheme," in Proc. IEEE Int. Symp. Circuits and Systems, pp. 671-674, 2002.

- [5] T. Saeki, K. Minami, H. Yoshida, and H. Suzuki, "A direct-skew-detect synchronous mirror delay for application-specific integrated circuits," IEEE J. Solid-State Circuits, vol. 34, pp. 372-379, Mar. 1999.